## Exercise 1

Minimize the Boolean equation for the control of the segment 1 in the following seven-segment display, using Karnaugh maps.

The inputs of the circuit are the four variables **a b c d** representing the bits of the number from 0 to 9 to be represented, with **a** the most significant bit and **d** the least significant bit. The output of the circuit is the output **Z** which needs to be equal to '1' when the segment 1 in the figure above needs to be illuminated and '0' otherwise.

Highlight the following steps:

a) Find the truth table of the required logic function

**b)** Minimize the function in Sum of Products (SOP) form using Karnaugh map method and properly considering the don't care conditions

c) Draw the corresponding logic circuit

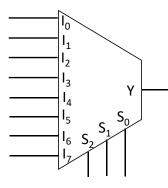

**d)** Realize the logic function through the 8-to-1 line-multiplexer in the figure. Clearly indicate how *a*, *b*, *c*, *d*, and *Z* should be connected to the mux.

## Solution Exercize 1:

## a) Truth table

| - |   |   |   |   |

|---|---|---|---|---|

| а | В | С | d | Z |

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | Х |

| 1 | 0 | 1 | 1 | Х |

| 1 | 1 | 0 | 0 | Х |

| 1 | 1 | 0 | 1 | Х |

| 1 | 1 | 1 | 0 | Х |

| 1 | 1 | 1 | 1 | Х |

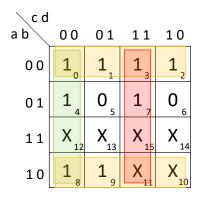

**b)** Minimized function in Sum of Products (SOP) form:

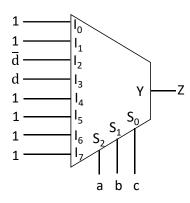

**d)** Implementation with 8-to-1 line-mux (note: due to don't care conditions, there are multiple correct implementations)

## Exercise 2

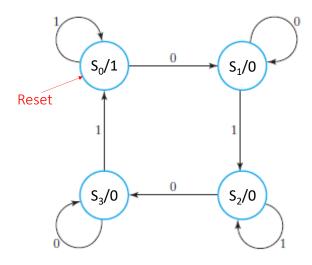

Consider the sequential system described by the state diagram below, with input x and output z.

Answer to the following questions:

- a) Is this a Mealy or a Moore machine? Motivate your answer

- **b)** Find the state transition and output table

- c) What is the minimum number of flip-flops needed to implement the system? How many flip-flops are needed to implement the system using a 1-hot encoding for the states?

- d) Describe the system in VHDL, using positive edge triggered D-Flip-Flops.

Solution Exercize 2:

a) It's a Moore machine, as the output depends only on the current state and not on the input.

**b)** State transitions and output table

| Present               | Future state   |                | Output |

|-----------------------|----------------|----------------|--------|

| state                 | X = 0          | X = 1          | Z      |

| S <sub>0</sub>        | S <sub>1</sub> | S <sub>0</sub> | 1      |

| <b>S</b> <sub>1</sub> | S <sub>1</sub> | S <sub>2</sub> | 0      |

| S <sub>2</sub>        | S <sub>3</sub> | S <sub>2</sub> | 0      |

| <b>S</b> <sub>3</sub> | S <sub>3</sub> | S <sub>0</sub> | 0      |

- c) The minimum number of bits needed to represent the states of the system is 2. 4 filp-flops are needed to implement the system using a 1-hot encoding representation for the states.

- d) A possible VHDL description is a behavioral one:

```

library IEEE;

use IEEE.std_logic_1164.all;

entity seq is

port (clk, rst, X: in std_logic;

Z: out std logic);

end seq;

architecture beh of seq is

type state type is (S0, S1, S2, S3);

signal state, next state: state type;

begin

-- Process 1: Updates state and implements asynchronous reset

state_register: process (rst, clk)

begin

if (rst = '1') then

state <= S0;</pre>

elsif (clk'event and clk = '1') then

state <= next state;</pre>

end if;

end process;

-- Process 2: Computes the next state (function of input and present state)

next_state_comb: process (X, state)

begin

case state is

when SO =>

if X = '0' then

next_state <= S1;</pre>

else

next state <= S0;</pre>

end if;

when S1 =>

if X = '0' then

next_state <= S1;</pre>

else

next_state <= S2;</pre>

end if;

when S2 =>

if X='0' then

next_state <= S3;</pre>

```

```

else

next_state <= S2;</pre>

end if;

when S3 =>

if X='0' then

next_state <= S3;</pre>

else

next_state <= S0;</pre>

end if;

end case;

end process;

-- Process 3: calculates the output (function of the state)

output_comb: process (state)

begin

if (state = SO) then

Z <= '1'

else

Z <= '0';

end if;

end process;

end beh;

```